# Intel<sup>®</sup> Server System M50CYP1UR Family

## **Technical Product Specification**

An overview of product features, functions, architecture, and support specifications.

Rev. 1.2 June 2021

<This page intentionally left blank>

## **Document Revision History**

| Date      | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| May 2021  | 1.0      | Initial production release                                                                                                                                                                                                                                                                                                                                                                        |

| May 2021  | 1.1      | <ul> <li>Section 4.3.1. Updated note following DDR4 DIMM Support Disclaimer</li> <li>Minor updates throughout for clarity</li> </ul>                                                                                                                                                                                                                                                              |

| June 2021 | 1.2      | <ul> <li>Table 1. Updated table</li> <li>Table 2. Updated table         <ul> <li>Updated Chipset row</li> <li>Added Server Management Processor row</li> </ul> </li> <li>Table 8. Updated row for Silver 4300 processors</li> <li>Section 7.3.3. Updated section to remove "NVMe" from riser card name.</li> <li>Updated Section 9.3.4.2</li> <li>Minor updates throughout for clarity</li> </ul> |

#### **Disclaimers**

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software, or service activation. Performance varies depending on system configuration. No computer system can be absolutely secure. Check with your system manufacturer or retailer or learn more at intel.com.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness

for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or by visiting <a href="https://www.intel.com/design/literature.htm">www.intel.com/design/literature.htm</a>.

Intel, Xeon, SpeedStep, Intel Optane, and the Intel logo are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

© Intel Corporation

## **Table of Contents**

| 1. Introd | uction                                                                  | 13 |

|-----------|-------------------------------------------------------------------------|----|

| 1.1       | Reference Documents and Support Collaterals                             | 14 |

| 2. Server | System Family Overview                                                  | 16 |

| 2.1       | Server System Feature Set                                               | 16 |

| 2.2       | System Feature Identification                                           | 19 |

| 2.3       | Front Drive Bay Options                                                 | 20 |

| 2.4       | Server Board Features                                                   | 20 |

| 2.5       | System Dimensional Data                                                 | 25 |

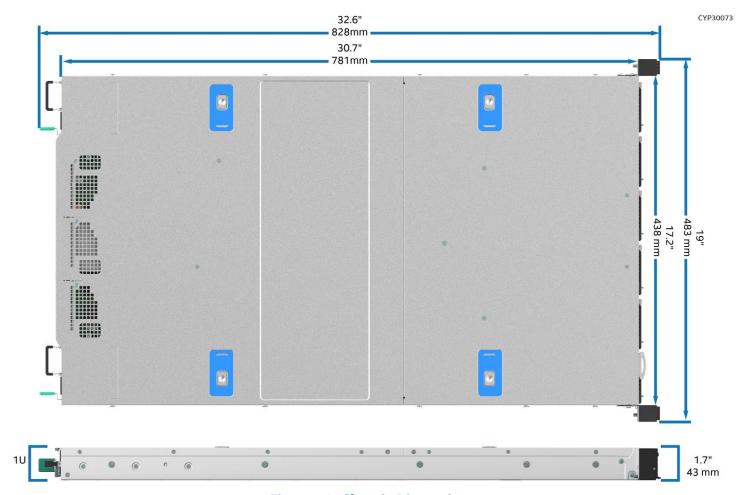

| 2.5.1     | Chassis Dimensions                                                      | 25 |

| 2.5.2     | Label Emboss Dimensions                                                 | 26 |

| 2.5.3     | Pull-Out Tab Label Emboss Dimensions                                    | 26 |

| 2.6       | System Top Cover Usage                                                  | 27 |

| 2.7       | System Cable Routing Channels                                           | 29 |

| 2.8       | Available Rack and Cabinet Mounting Kit Options                         | 30 |

| 2.9       | System Level Environmental Limits                                       | 30 |

| 2.10      | System Packaging                                                        | 31 |

| 3. Proces | sor Support                                                             | 33 |

| 3.1       | Processor Heat Sink Module (PHM) Assembly and Processor Socket Assembly |    |

| 3.2       | Processor Thermal Design Power (TDP) Support                            | 34 |

| 3.3       | Processor Family Overview                                               | 35 |

| 3.3.1     | Supported Technologies                                                  | 36 |

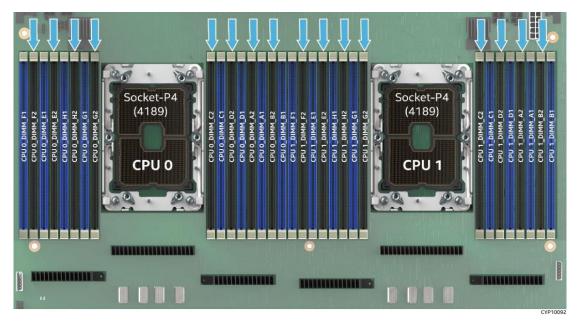

| 3.4       | Processor Population Rules                                              | 37 |

| 4. Memo   | ry Support                                                              | 38 |

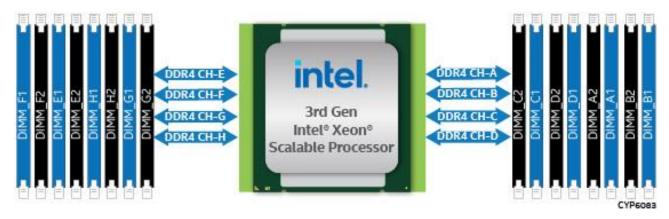

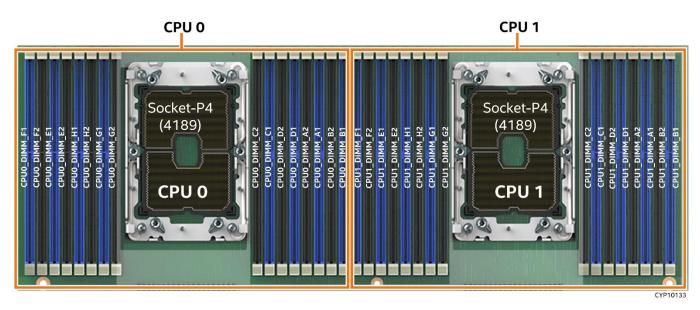

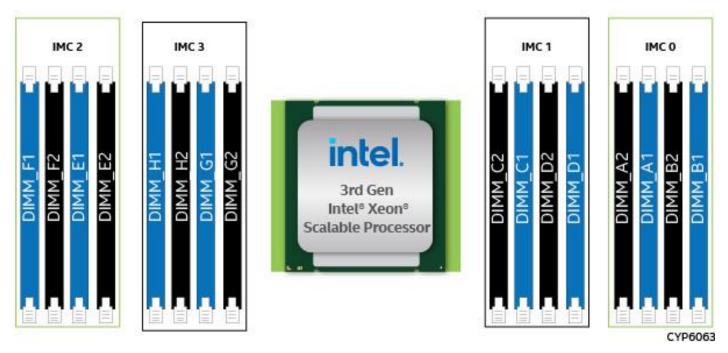

| 4.1       | Memory Subsystem Architecture                                           | 38 |

| 4.2       | Supported Memory                                                        | 38 |

| 4.2.1     | Standard DDR4 DIMM Support                                              | 39 |

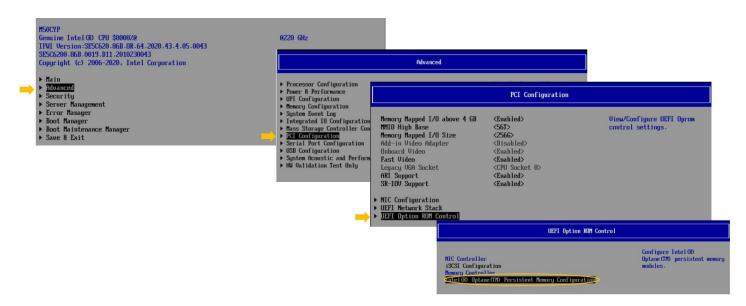

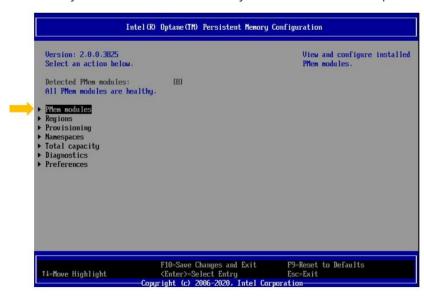

| 4.2.2     | Intel® Optane™ Persistent Memory 200 Series Module Support              | 40 |

| 4.3       | Memory Population                                                       | 42 |

| 4.3.1     | DDR4 DIMM Population Rules                                              | 43 |

| 4.3.2     | Intel® Optane™ Persistent Memory 200 Series Module Rules                | 44 |

| 4.3.3     | Recommended Memory Configurations                                       | 46 |

| 4.4       | Memory RAS Support                                                      | 48 |

| 5. Systen | n Power                                                                 | 51 |

| 5.1       | Power Supply Configurations                                             | 52 |

| 5.1.1     | Single Power Supply (1+0) Power Configuration                           |    |

| 5.1.2     | Dual Power Supply 1+1 Power Configuration                               | 52 |

| 5.1.3     | Dual Power Supply 2+0 Power Configuration                               | 53 |

| 5.2       | Closed Loop System Throttling (CLST)                                    | 53 |

| 5.3       | Smart Ride Through (SmaRT) Throttling                                   | 53 |

| 5.4        | Power Supply Cold Redundancy                                  | 54 |

|------------|---------------------------------------------------------------|----|

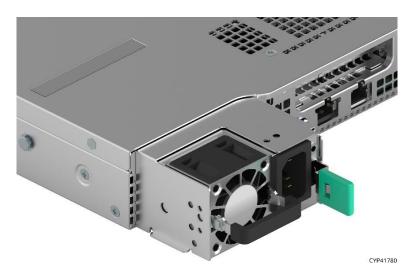

| 5.5        | Power Supply Specification Overview                           |    |

| 5.5.1      | Power Supply Module Efficiency                                | 54 |

| 5.5.2      | AC Power Cord Specifications                                  | 55 |

| 5.6        | AC Power Supply Features                                      | 55 |

| 5.6.1      | Power Supply Status LED                                       | 55 |

| 5.6.2      | Protection Circuits                                           | 56 |

| 6. Therm   | al Management                                                 | 57 |

| 6.1        | Thermal Operation and Configuration Requirements              | 58 |

| 6.2        | Thermal Management Overview                                   | 59 |

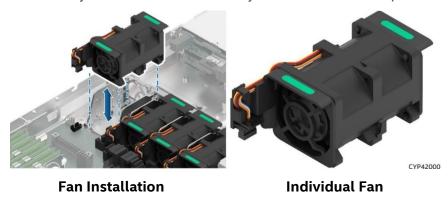

| 6.3        | System Fans                                                   | 60 |

| 6.4        | Power Supply Module Fans                                      | 61 |

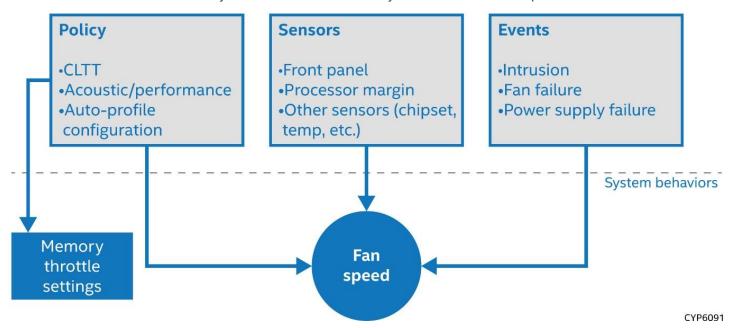

| 6.5        | Fan Speed Control                                             | 61 |

| 6.5.1      | Programmable Fan Pulse Width Modulation (PWM) Offset          | 61 |

| 6.5.2      | Hot-Swappable Fans                                            | 62 |

| 6.5.3      | Fan Redundancy Detection                                      | 62 |

| 6.5.4      | Fan Domains                                                   | 62 |

| 6.5.5      | Nominal Fan Speed                                             | 62 |

| 6.5.6      | Thermal and Acoustic Management                               | 63 |

| 6.5.7      | Thermal Sensor Input to Fan Speed Control                     | 63 |

| 6.6        | FRUSDR Utility (FRU)                                          | 64 |

| 7. PCle* / | Add-in Card Support                                           | 65 |

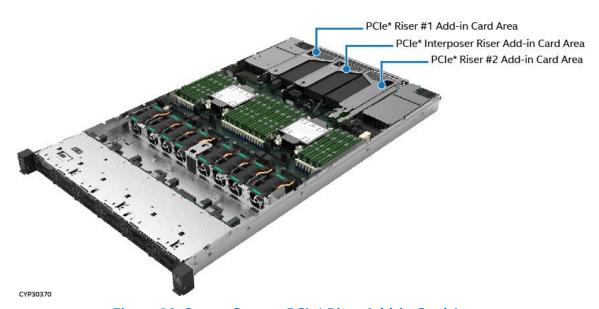

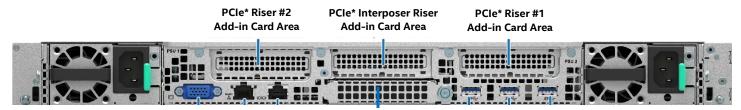

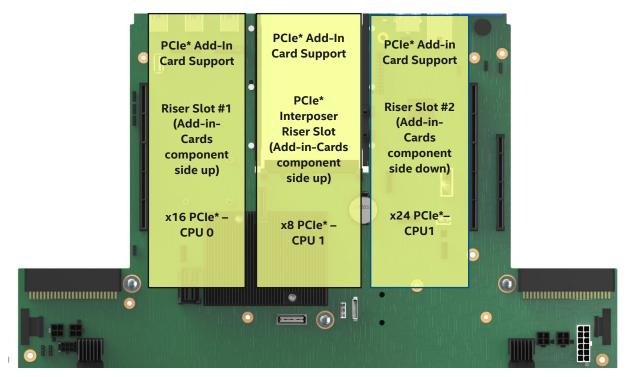

| 7.1        | PCIe* Riser Card Support                                      | 66 |

| 7.1.1      | PCI Express Bifurcation                                       | 67 |

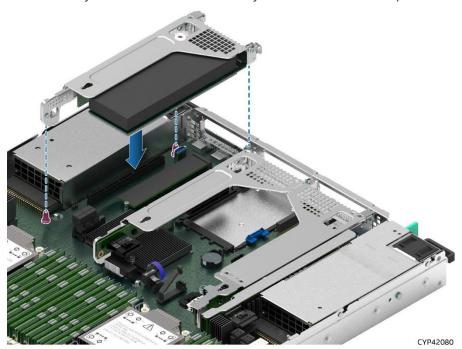

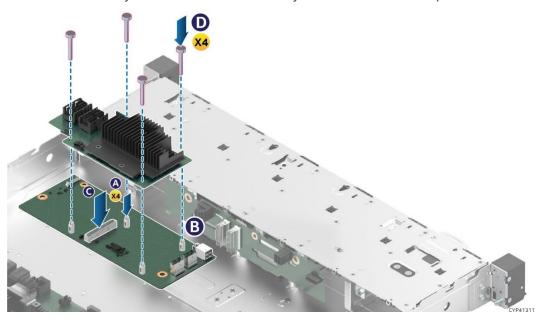

| 7.2        | Riser Card Assembly                                           | 68 |

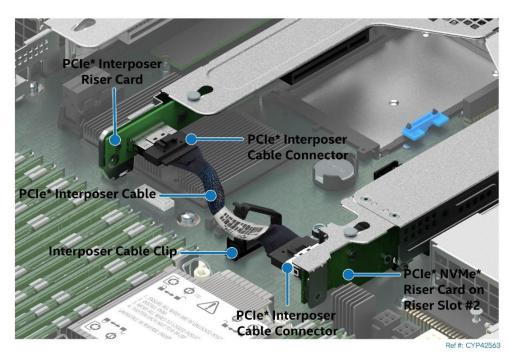

| 7.3        | PCIe* Riser Card and Interposer Card Options                  |    |

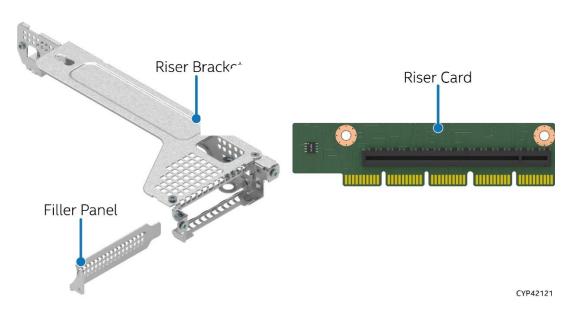

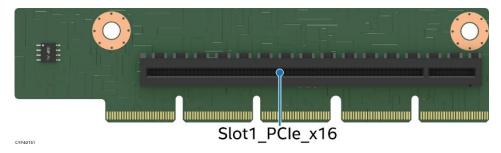

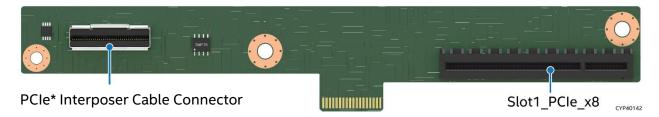

| 7.3.1      | PCIe* Riser Card for Riser Slot #1 (iPC – CYP1URISER1STD)     | 70 |

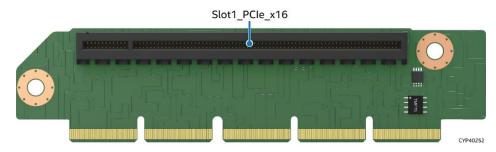

| 7.3.2      | PCIe* Riser Card for Riser Slot #2 (iPC – CYP1URISER2STD)     | 71 |

| 7.3.3      | PCIe* Riser Card for Riser Slot #2 (iPC – CYP1URISER2KIT)     | 71 |

| 7.3.4      | PCIe* Interposer Card (iPC – CYP1URISER2KIT)                  | 72 |

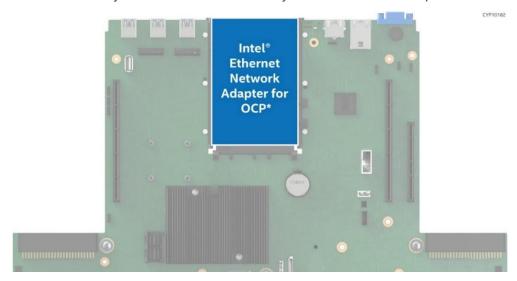

| 7.4        | Intel® Ethernet Network Adapter for OCP* Support              | 74 |

| 8. Systen  | n Storage                                                     | 77 |

| 8.1        | Front Drive Bay Support                                       | 77 |

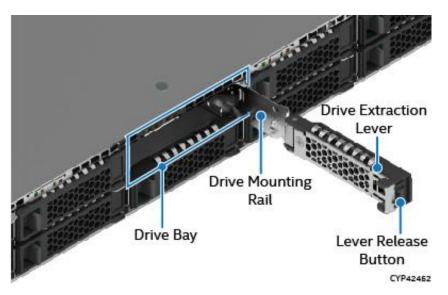

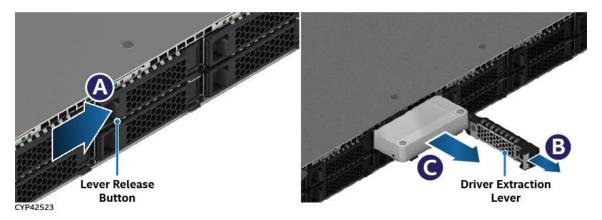

| 8.1.1      | Hot Swap Drives and Drive Mounting Rail Support               | 78 |

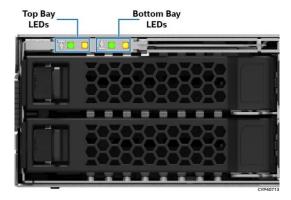

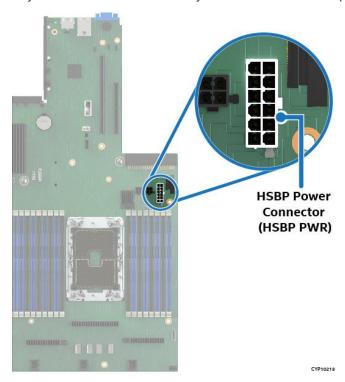

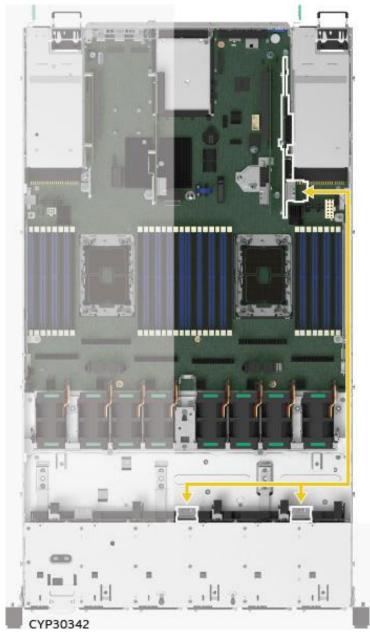

| 8.1.2      | Hot Swap Backplane (HSBP) Support                             | 83 |

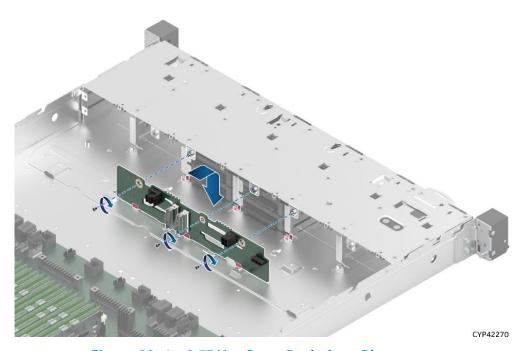

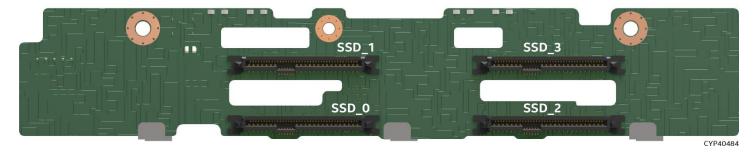

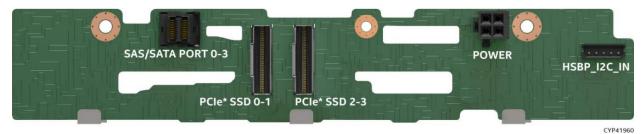

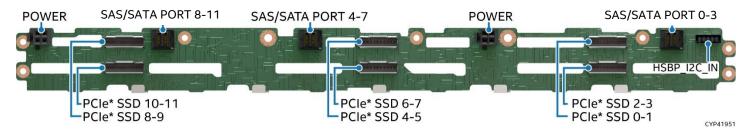

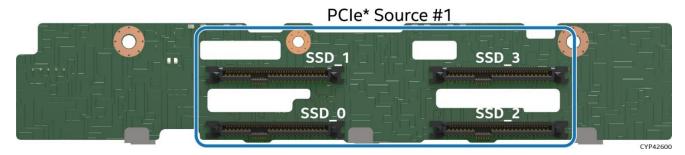

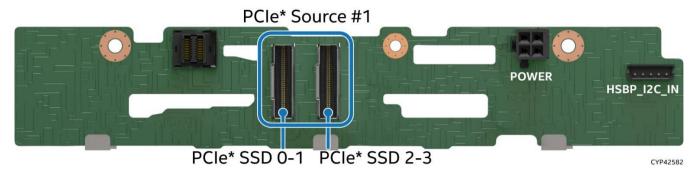

| 8.1.3      | 4 x 2.5" Drive SATA/SAS/NVMe* Combo Backplane                 | 85 |

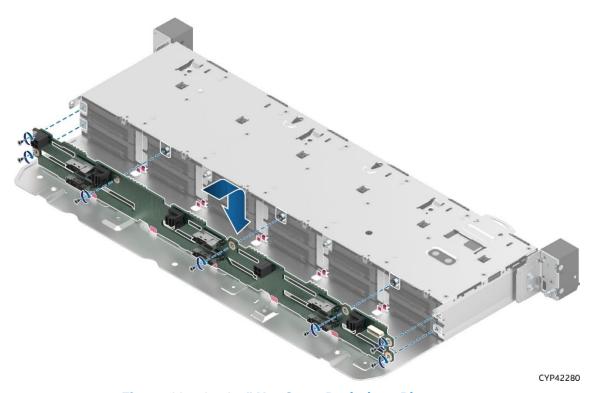

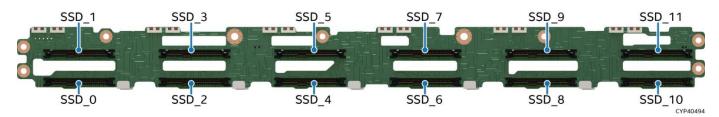

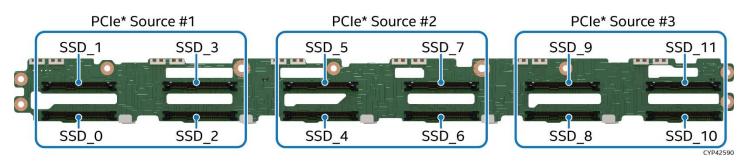

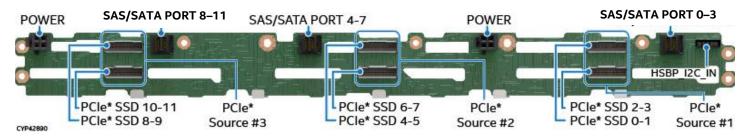

| 8.1.4      | 12 x 2.5" Drive SATA/SAS/NVMe* Combo Backplane                | 87 |

| 8.2        | NVMe* Storage Support                                         | 88 |

| 8.2.1      | PCIe* SlimSAS* Support                                        | 88 |

| 8.2.2      | PCIe* NVMe* Riser Card for Riser Slot #3 (iPC – CYPRISER3RTM) | 89 |

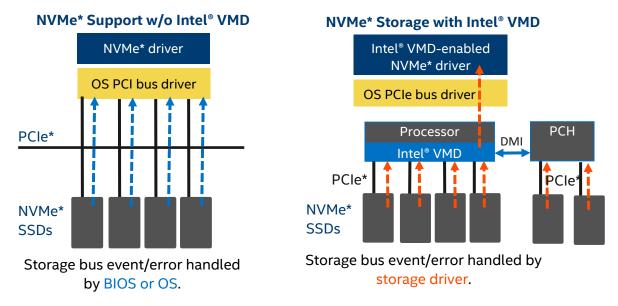

| 8.2.3      | Intel® Volume Management Device (Intel® VMD) 2.0 for NVMe*    | 91 |

| 8.2.4        | Intel® Virtual RAID on Chip (Intel® VROC) for NVMe*    | 92  |

|--------------|--------------------------------------------------------|-----|

| 8.2.5        | NVMe* Drive Population Rules for Intel® VROC 7.5       | 93  |

| 8.3          | Server Board SATA Support                              | 95  |

| 8.3.1        | SATA Support Through Mini-SAS HD Connectors            | 96  |

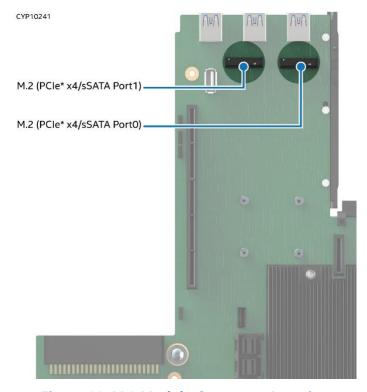

| 8.3.2        | SATA Support Through M.2 Connectors                    | 96  |

| 8.3.3        | Staggered Disk Spin-Up                                 | 96  |

| 8.3.4        | Intel® Virtual RAID on Chip (Intel® VROC) for SATA     | 97  |

| 8.4          | SAS Storage Support                                    | 98  |

| 8.4.1        | SAS Interposer Card (iPC – CYPSASMODINT) Support       | 98  |

| 8.5          | M.2 SSD Storage Support                                | 100 |

| 9. Front C   | ontrol Panel and I/O                                   | 101 |

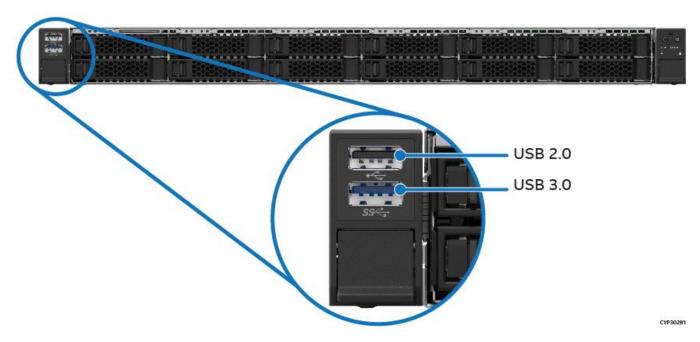

| 9.1          | Control Panel Features                                 | 101 |

| 9.2          | Front I/O Features                                     | 104 |

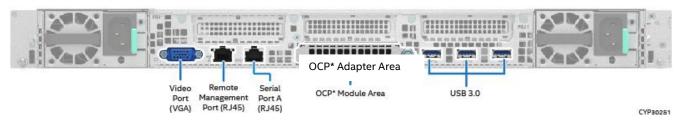

| 9.3          | Rear I/O Features                                      | 104 |

| 9.3.1        | Remote Management Port                                 | 104 |

| 9.3.2        | Serial Port Support                                    | 105 |

| 9.3.3        | USB Support                                            | 107 |

| 9.3.4        | Video Support                                          | 108 |

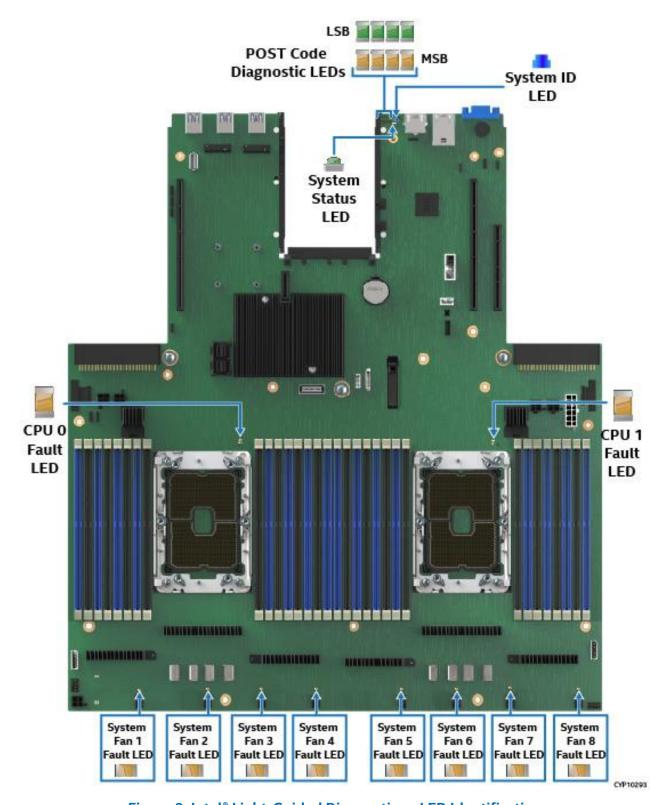

| 10. Intel® L | ight Guided Diagnostics                                | 110 |

| 10.1         | Server Board Light Guided Diagnostics                  | 110 |

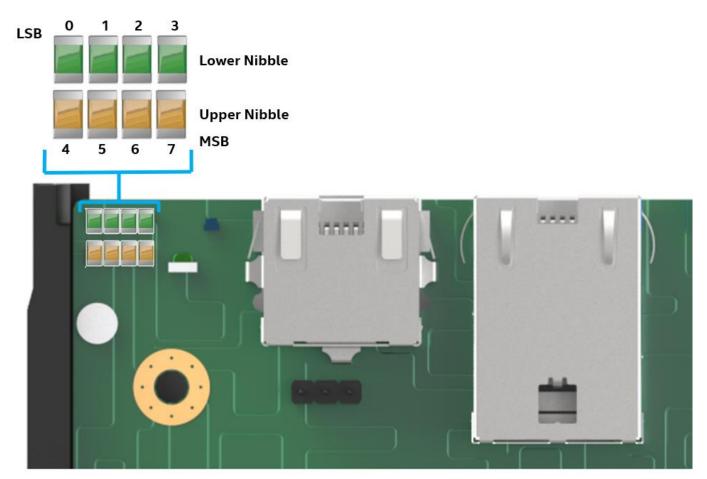

| 10.1.1       | Post Code Diagnostic LEDs                              | 111 |

| 10.1.2       | System ID LED                                          | 111 |

| 10.1.3       | System Status LED                                      | 111 |

| 10.1.4       | BMC Boot/Reset Status LED Indicators                   | 111 |

| 10.1.5       | Processor Fault LEDs                                   | 112 |

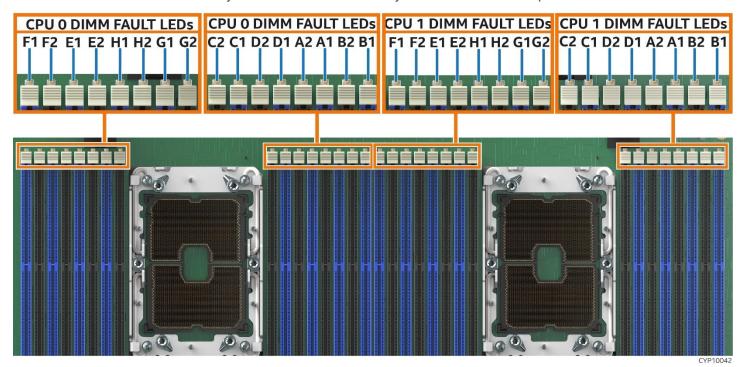

| 10.1.6       | Memory Fault LEDs                                      | 112 |

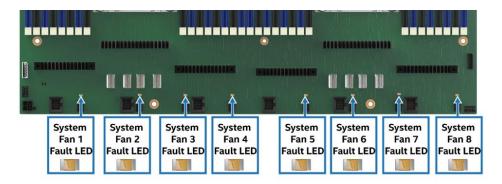

| 10.1.7       | Fan Fault LEDs                                         | 113 |

| 10.2         | Additional Light Guided Diagnostics                    | 113 |

| 10.2.1       | Power Supply Status LED                                | 113 |

| 10.2.2       | Front Panel Control LED Indicators                     | 113 |

| 10.2.3       | Drive Bay LEDs                                         | 113 |

| 10.2.4       | Drive Activity LED for Front Control Panel             | 113 |

| Appendix A   | . Getting Help                                         | 114 |

| Appendix B   | Integration and Usage Tips                             | 115 |

| Appendix C   | . Post Code Diagnostic LED Decoder                     | 116 |

| C.1          | Early POST Memory Initialization MRC Diagnostic Codes  | 117 |

| C.2          | BIOS POST Progress Codes                               |     |

| Appendix D   | ). Post Error Codes                                    | 122 |

| D.1          | POST Error Beep Codes                                  | 128 |

| D.2          | Processor Initialization Error Summary                 | 129 |

| Appendix E   | . System Configuration Table for Thermal Compatibility | 131 |

| E.1 No              | rmal Operating Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 131 |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                     | n Fail Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| Appendix F.         | System Sensors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 139 |

| • •                 | Statement of Volatility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|                     | Product Regulatory Compliance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|                     | Glossary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|                     | , and the second |     |

| List of Fig         | gures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

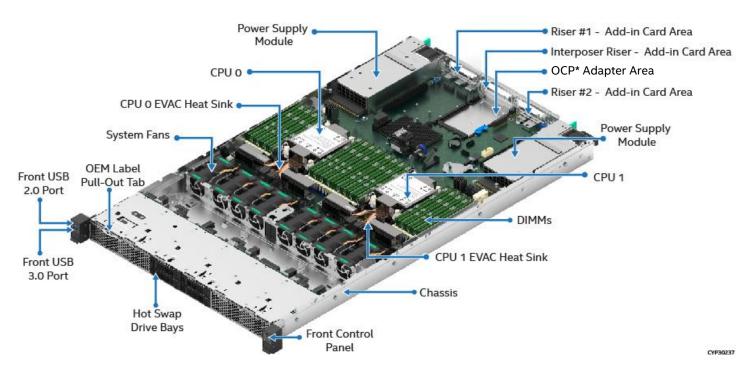

| Figure 1. Intel® \$ | Server System M50CYP1UR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13  |

| _                   | System Components Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

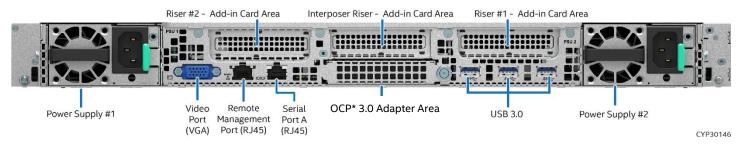

| Figure 3. Back P    | anel Feature Identification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19  |

| Figure 4. Front (   | Control Panel Feature Identification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 20  |

| Figure 5. 4 x 2.5   | " Front Drive Bay Configuration – M50CYP1UR204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20  |

| Figure 6. 12 x 2.   | 5" Front Drive Bay Configuration – M50CYP1UR212                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20  |

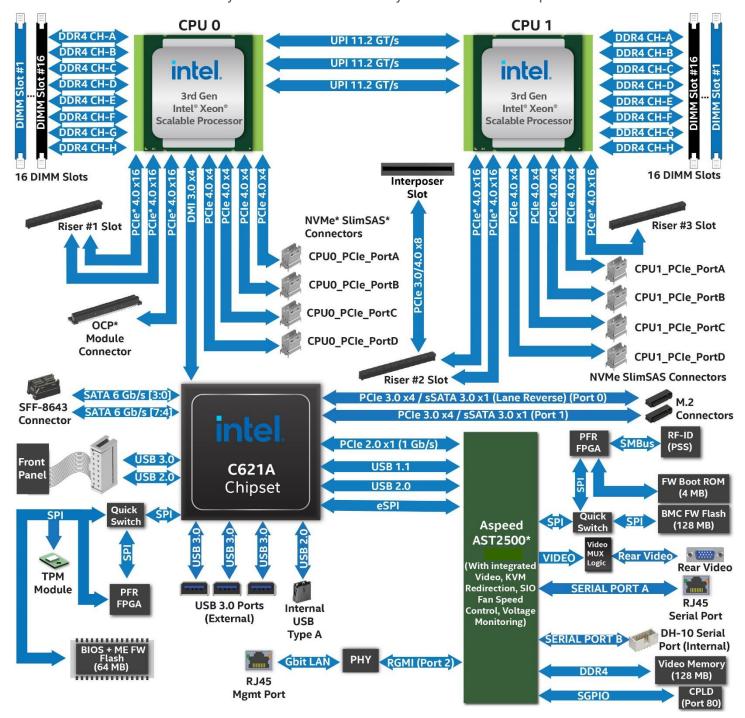

| Figure 7. Intel® 5  | Server Board M50CYP2SB1U Architectural Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 21  |

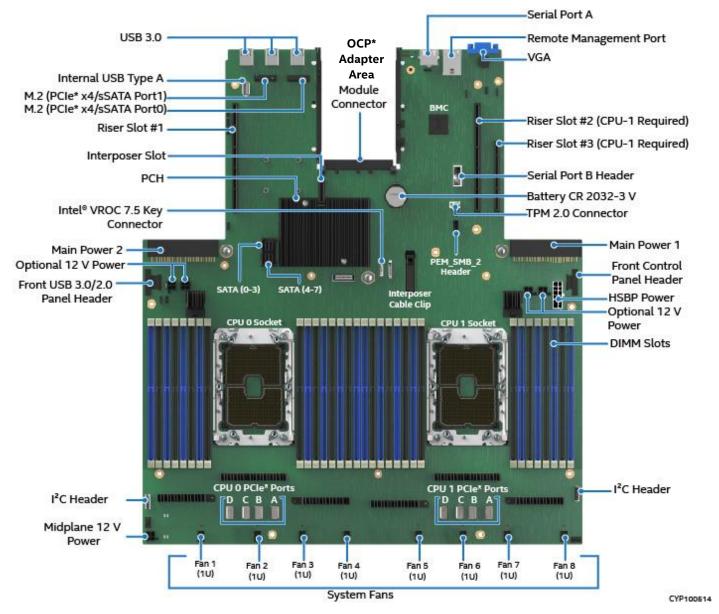

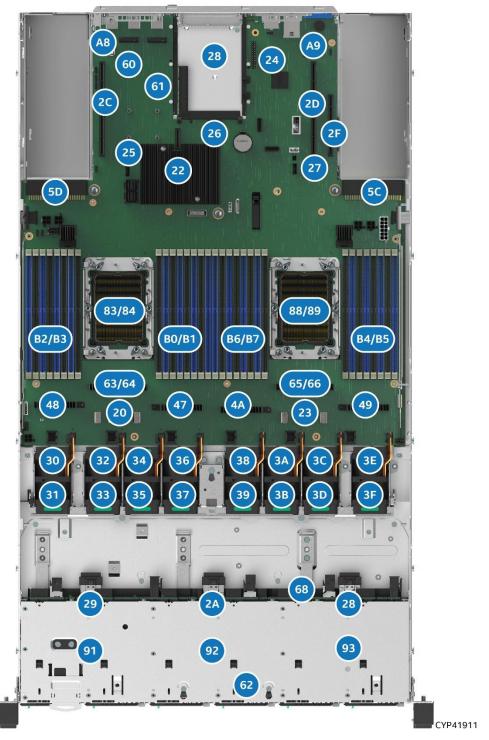

| Figure 8. Intel® 9  | Server Board M50CYP2SB1U Component / Feature Identification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22  |

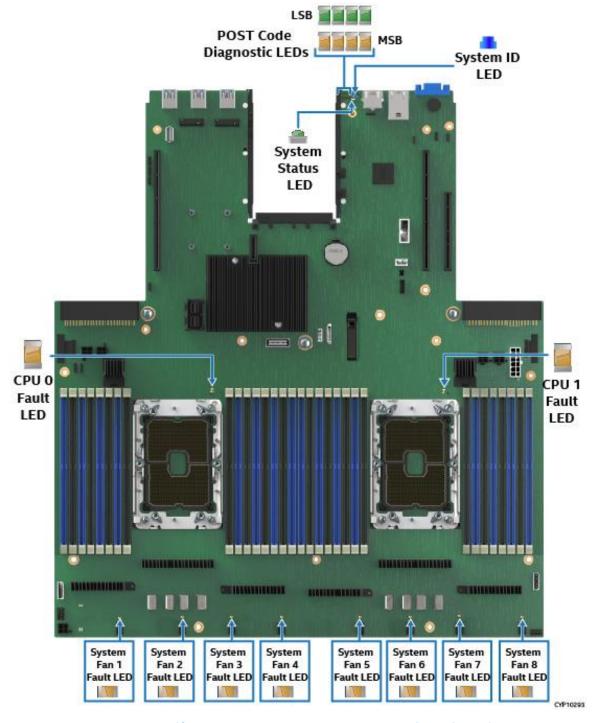

| Figure 9. Intel® I  | ight-Guided Diagnostics – LED Identification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23  |

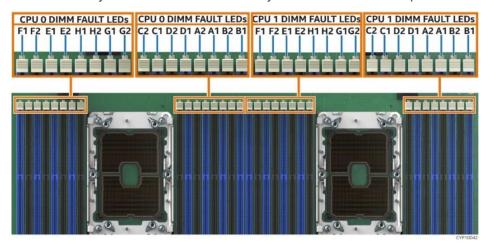

| Figure 10. Intel®   | Light-Guided Diagnostics – DIMM Fault LEDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24  |

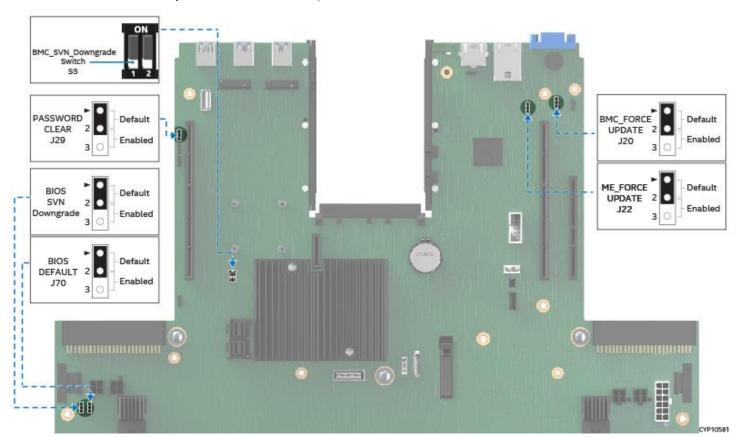

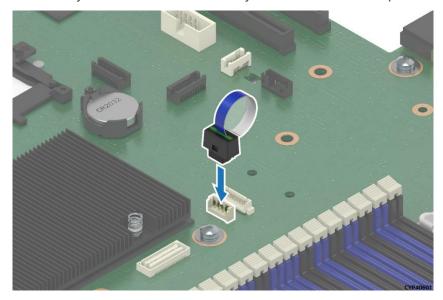

| Figure 11. Syste    | m Configuration and Recovery Jumpers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24  |

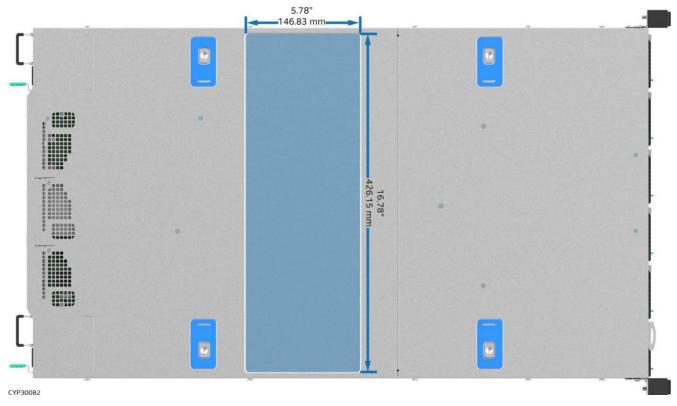

| Figure 12. Chass    | sis Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25  |

| Figure 13. Label    | Emboss Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26  |

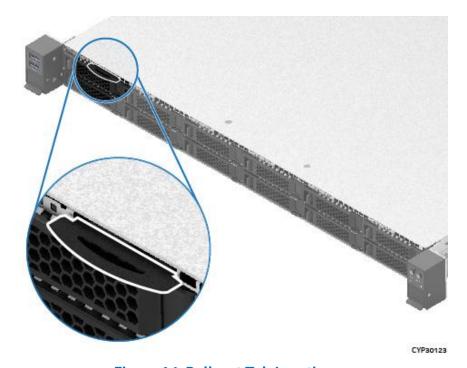

| J                   | out Tab Location                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

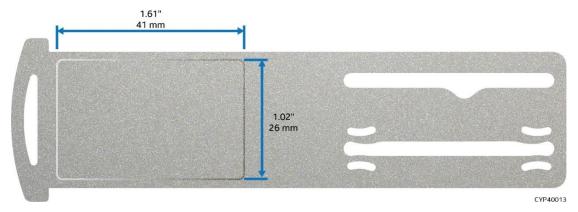

| Figure 15. Pull-    | out Fab Label Emboss Dimensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27  |

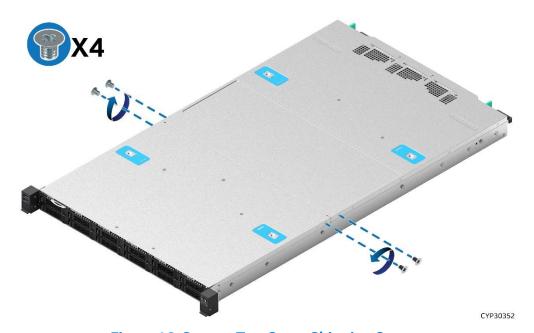

| -                   | m Top Cover Shipping Screws                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

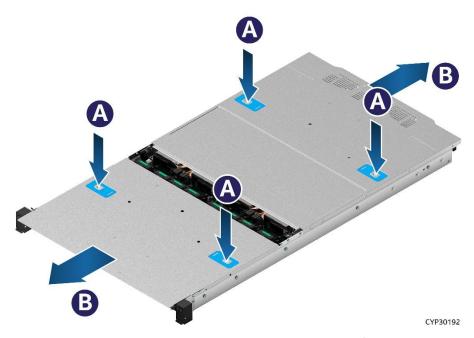

|                     | m Top Cover Removal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|                     | m Top Cover Installation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

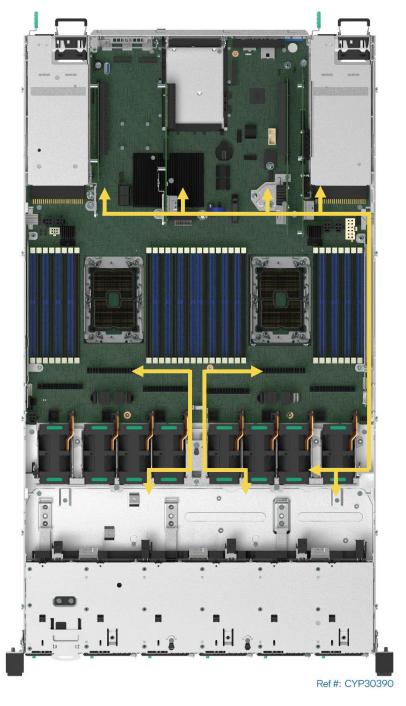

| •                   | m Cable Routing Channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

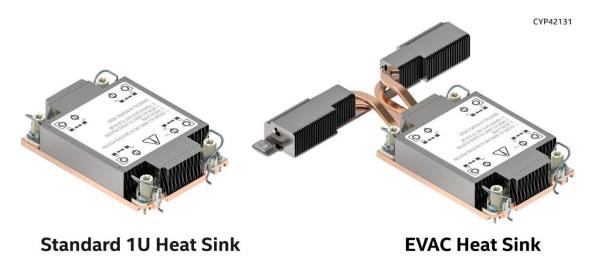

| -                   | orted Processor Heat Sinks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

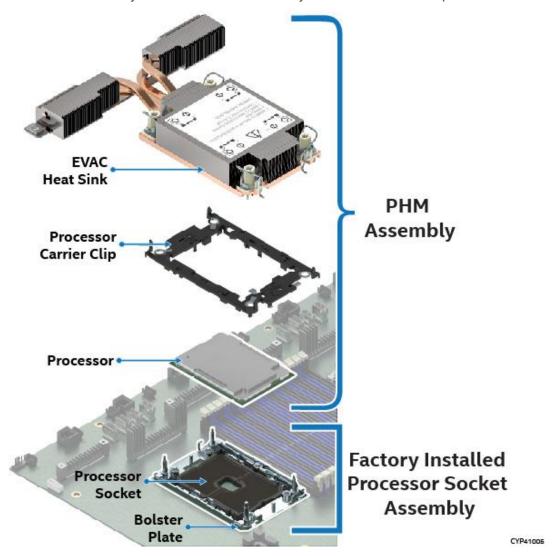

| _                   | Components and Processor Socket Reference Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

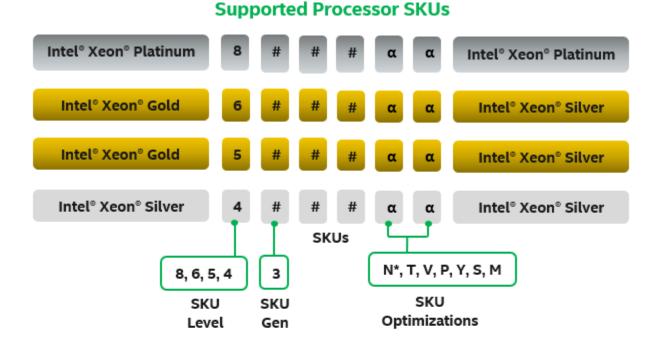

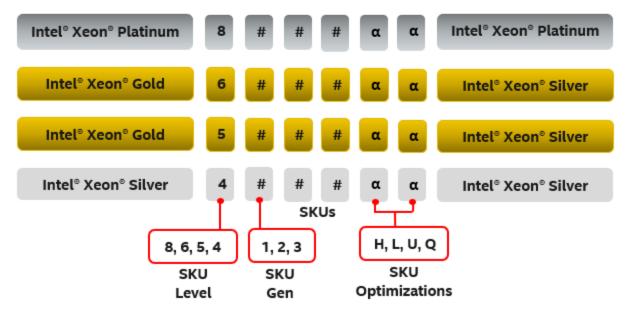

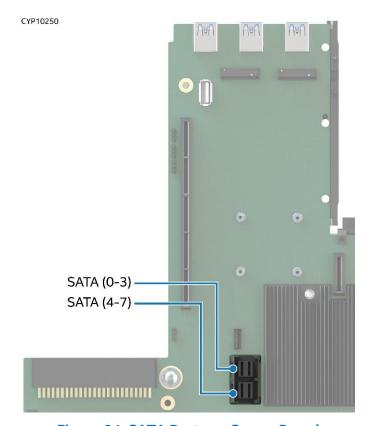

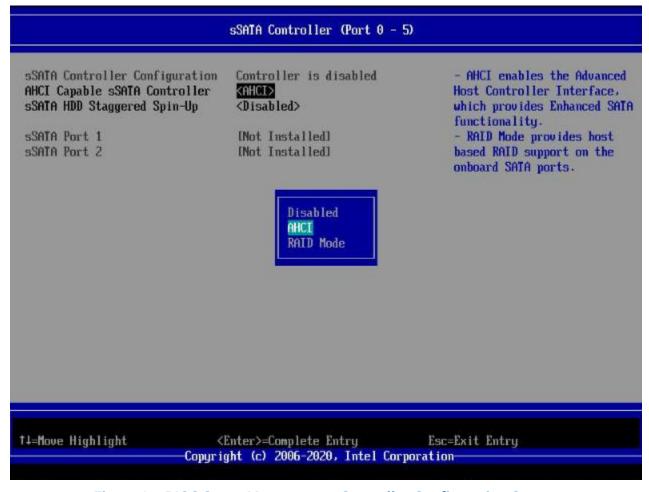

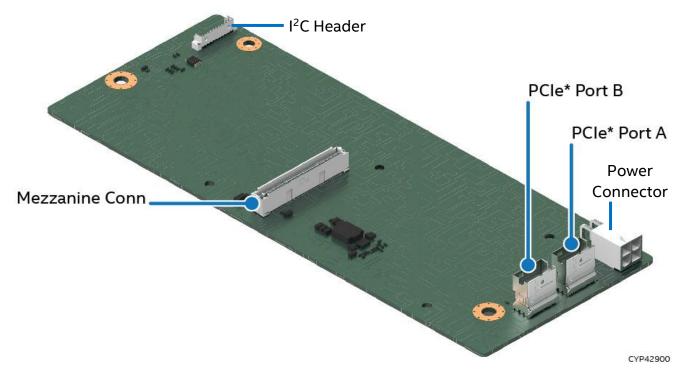

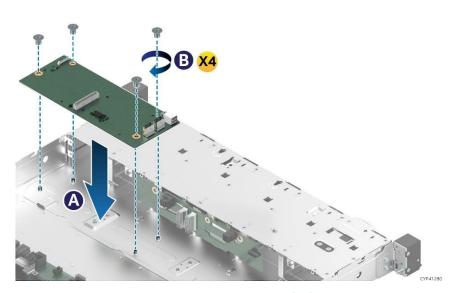

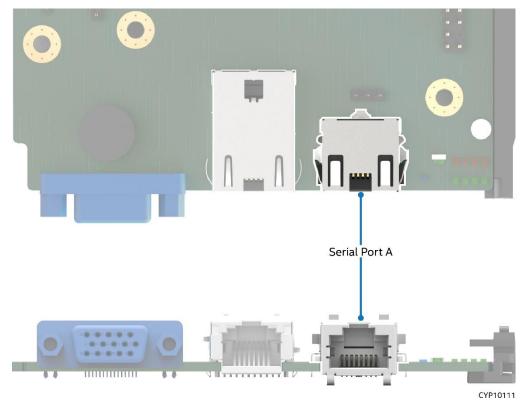

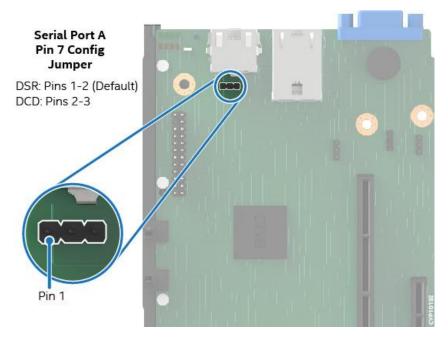

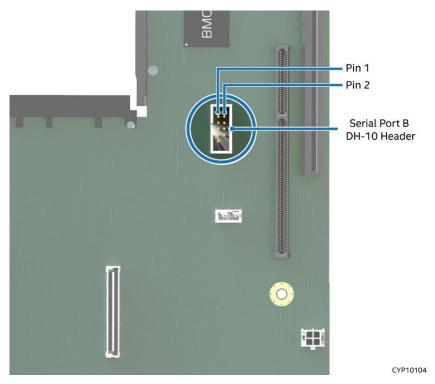

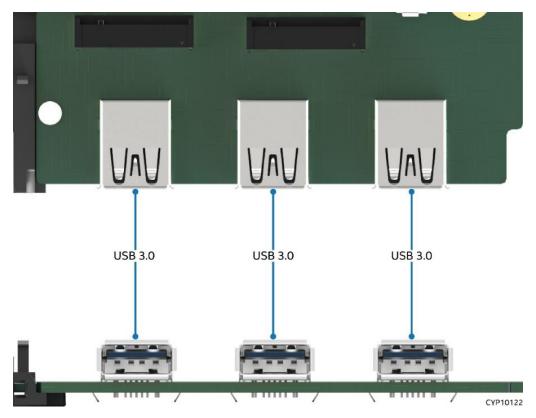

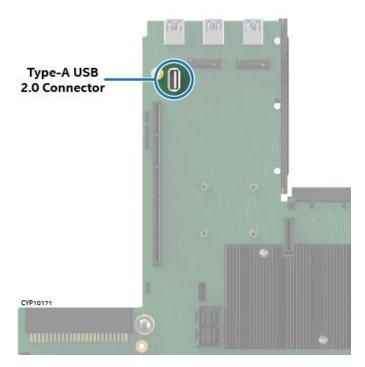

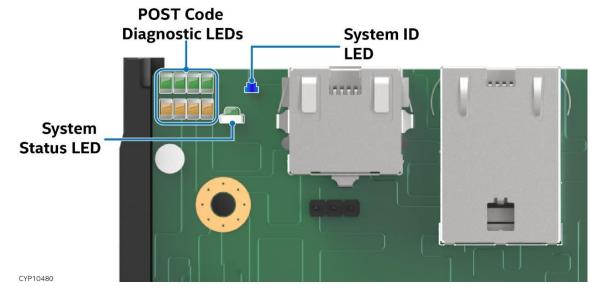

| _                   | en Intel® Xeon® Scalable Processor Identification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |